远程抄表硬件设计

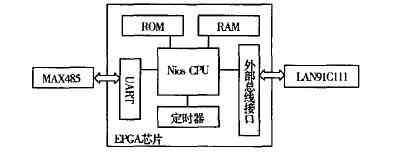

从图1中可以看出,数据集中器是系统中的关键部分,一方面它需要按照《DL/T64521997:多功能电能表通信规约》通过RS485总线从电表处采集数据,并执行各种控制任务;另一方面它必须能够解释以HTTP形式发送过来的控制命令,并将执行结果以HTML文件的形式返回给抄表客户端。 本文在进行硬件设计的时候采用了基于IP核的设计方法,并将数据集中器的大部分功能在单个FPGA芯片上予以实现。设计电路原理图之前,必须根据系统需求选择合适的IP核。所谓IP核,是指那些以硬件形式(硅片版图)或者软件形式(用Verilog、VHDL描述的RTL或者门级模型)存在的、具有特定功能的硬件电路。IP核通常分为硬核、固核与软核三种。根据系统的硬件开发环境以及性能需求,本文选择了Altera公司开发的一系列软核产品,它们是用Verilog语言所描述的硬件模块,允许用户根据需要对各种参数进行配置,如数据通路带宽、优先进行速度优化还是资源优化等,因而应用非常灵活。系统所用到的软IP核产品有Nios CPU、ROM、RAM、定时器、通用异步收发器UART,以及用于外部功能扩展的Avalon总线模块,并将Nios CPU配置为32位字长模式,拥有256个通用寄存器,工作频率33MHz;UART配置为14400bPs的波特率,8位数据位,2位停止位,无奇偶校验。在确定了IP核并进行相应设置后,需要设计系统的电路原理图。图2表示了由各个IP模块组成的数据集中器内部硬件结构,其中的ROM用于存放用户程序,RAM作为程序运行时的存储空间,定时器为实时操作系统提供时钟中断功能,外部总线接口和UART负责与系统外部进行通信。它们将通过一条内部总线与Nios CPU相连,这样就构成了一个完整的嵌入式硬件系统。设计电路图后的下一步工作是选择合适的实现载体。基于IP核的设计方法通常使用FPGA芯片或者直接在硅片上实现。本文采用的是Altera公司APEX20KE系列FPGA芯片,能提供8000个左右的逻辑块资源和多达400Kb左右的ROM和RAM存储空间。由于FPGA芯片具有可反复更改的特性,因此有助于硬件系统的改进和不断升级。另外,通过对通信接口进行重构,例如将UART改为CAN总线控制器,可以使系统能与更多的硬件环境兼容。

图2 数据集中器的硬件结构

由于在FPGA芯片上构造电平转换电路和以太网物理层、MAC层电路较困难,本文将这些功能放到了FPGA芯片的外面,并分别使用MAX485和LAN91C111芯片来实现电平转换和以太网硬件接口功能。FPGA芯片内的UART模块和MAX485芯片共同完成与电表的数据通信任务,前者负责接收和发送数据,后者完成信号电平的转换。SMSC公司的LAN91C111是为了方便嵌入式应用系统连接到快速以太网而专门设计的,它实现了CSMA/CD协议的物理层和媒体访问控制层(MAC)两个部分,并可以很方便地与许多嵌入式处理器进行数据交换。